Multi-Gigabit SerDes PHY (PCIe Gen-4)

Overview

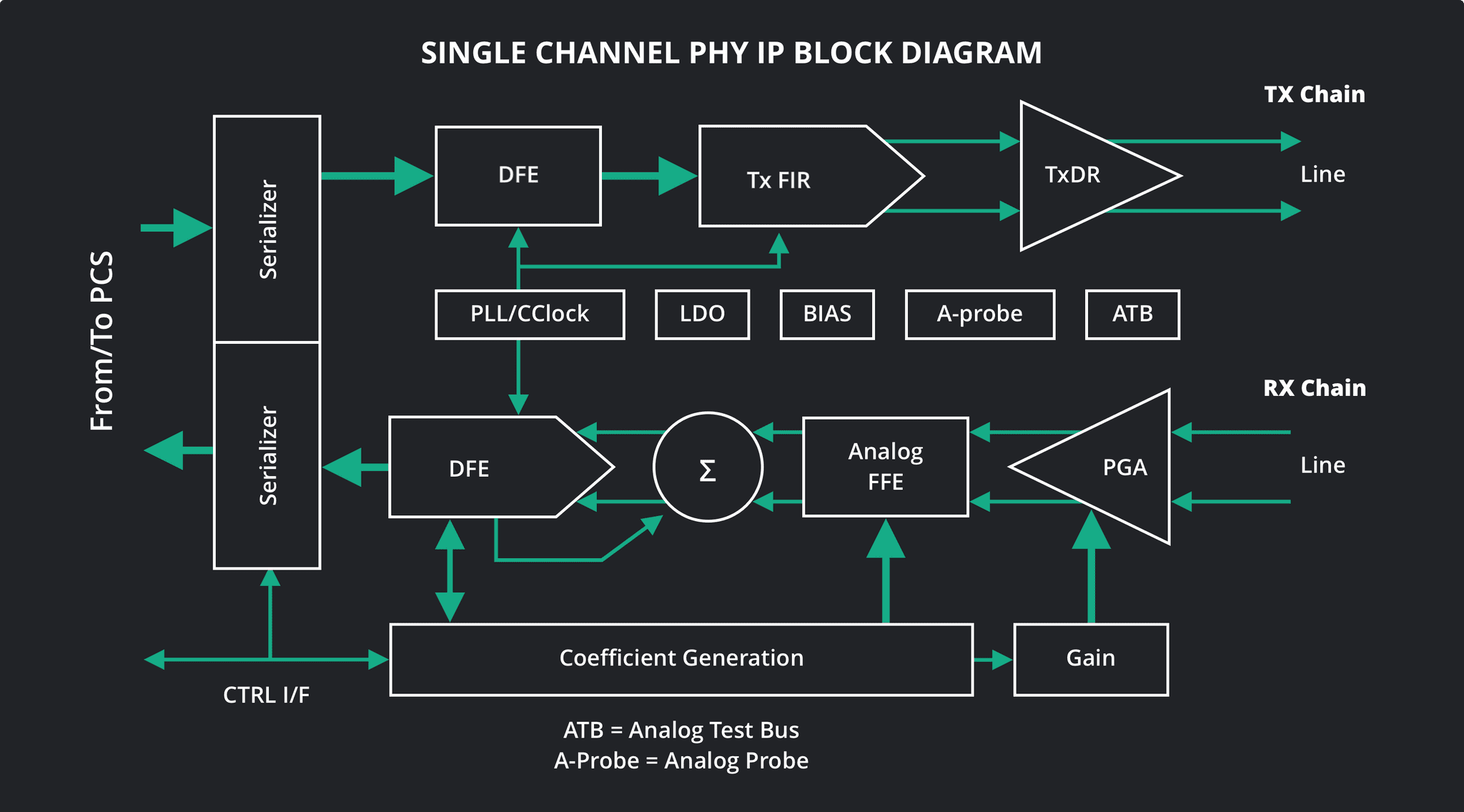

The multi-channel PHY IP can be used for high-speed chip-to-chip, board-to-board, and backplane interfaces. PCI Express® 4.0 and 10G-KR rates are supported while consuming extremely low power and area.

Due to patented adaptive analog and mixed-signal processing technology the PHY delivers Plug-and-Play grade Self-tuning capability whereby the user involvement in configuring IP and adjusting its operation for a specific application is greatly minimized. The fully-adaptive PHY architecture can tolerate process, voltage, temperature (PVT) and manufacturing variations while maintain sufficient performance margin, allowing implementations with standard CMOS digital processes.

The multi-tap transmitter and receiver equalizers, along with the advanced built-in diagnostics and ATE test vectors, enable customers to control, monitor and test for signal integrity without the need for expensive test equipment. This provides on-chip visibility into actual link and channel performance to quickly improve signal integrity. This capability reduces both product development cycles and the need for costly field support.

Key Features

- Speeds up to 16 Gbps, Protocol Agnostic

- ‘Plug and Play’ Self-tuning Architecture – Fully Adaptive Continuous Time Linear Equalizer (CTLE) with Decision Feedback Equalization (DFE).

- Spread-spectrum clocking (SRIS)

- Each PHY channel contains its own 7-, 9-, 11-, 15-, 23-, and 31-bit pseudo-random bit sequence (PRBS) generation for internal and external loopbacks

- Multi-channel PHY macro with single control and clock either internal or external reference

- Each channel is fully controllable via the integrated logic core as well as the test access port (TAP)

- Automated Test Equipment (ATE) test vectors for complete at-speed production testing

Deliverables

- Verilog models

- Liberty timing views (.lib)

- LEF abstracts (.lef)

- CDL netlist (.cdl)

- GDSII

- Documentation

Summary

- ‘Plug and Play’. Fully Adaptive Self-tuning Architecture – Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE). Supports various channel loss with no user configuration necessary. Channel loos 30dB+

- Embedded bit-to-error ratio tester (BERT) and internal SNR monitor

- Built-in Self-Test vectors, pseudo random bit sequencer (PRBS) generation and checker

- IEEE 1149.6 AC JTAG Boundary Scan

- Temperature range -40°C to 125°C @ junction

Target Applications

- Network switches and routers

- Automotive

- Embedded systems and set-top boxes

- Computing and storage networks

Technology

- Available in 28 nm TSMC

- Porting provided for customer specified processes including 16- and 7-nm FinFET technology