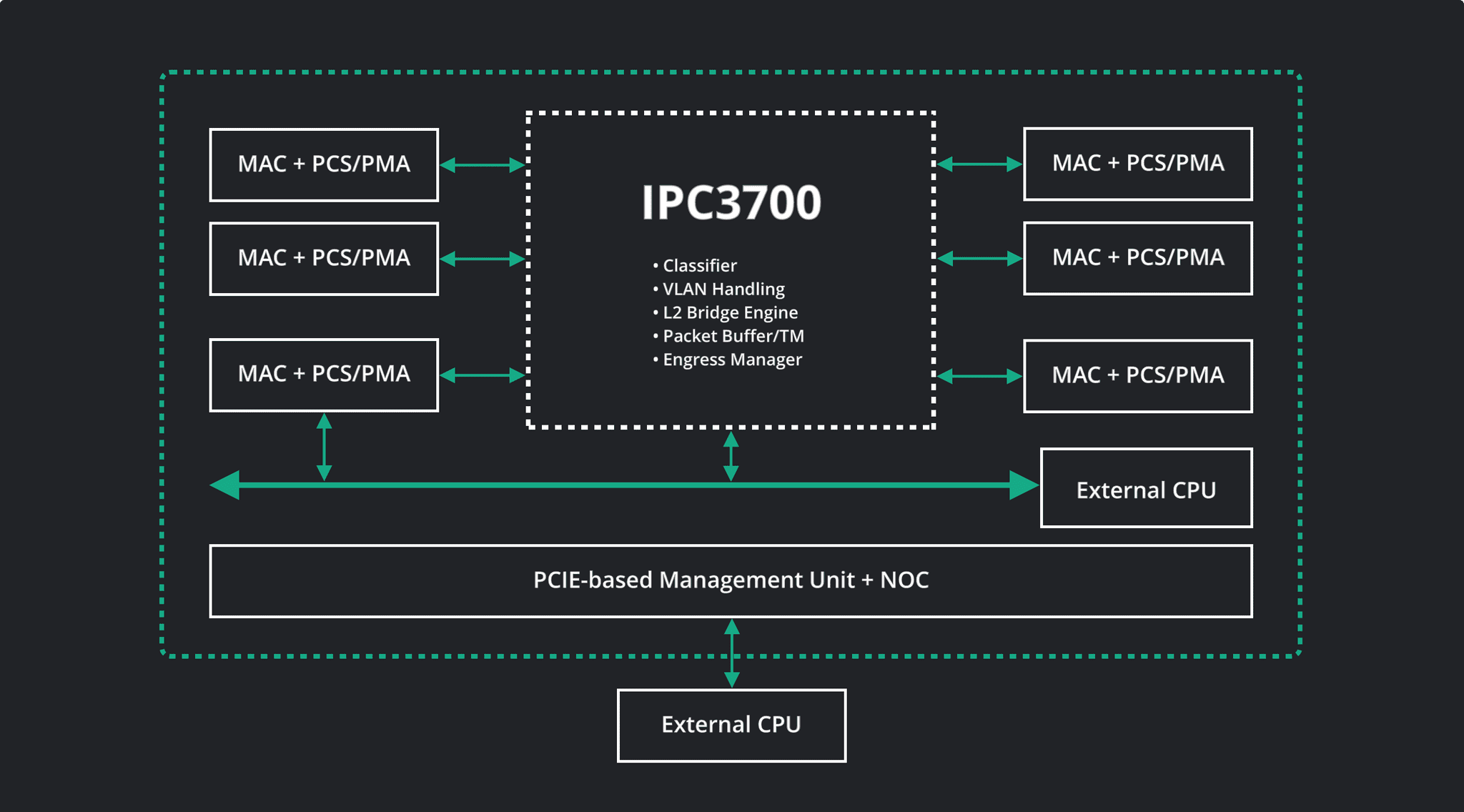

L2/L3 MANAGED SWITCH CORE

This product delivers scalability, deterministic performance, low latency, maximum flexibility and low power consumption.

Key Features

- Total bandwidth is up to 300Gbps (mid-size FPGA, worst case scenario).

- Up to 64 external ports.

- Each port can be configured as 10M/100M/1G/10G/25G/40G/100G Ethernet speed.

- Any combinations of external ports

- L2 layer bridge functionality, compatible with IEEE standard 802.1D Media Access Control (MAC) Bridges

- Status counters provide throughput statistics.

- Multicast support

- Supports VLAN 802.1Q (4K VLAN Table, ingress and egress filtering, tagging manipulations)

- Configurable priority per port (up to 8 queues per port)

- Store & Forward approach implemented

- Tail drop and WRED (Weighted Random Early Detection) mechanism used to drop packets during congestion.

- Automatic MAC addresses learning and aging control with configurable default time.

- Runtime S/W enabling for flooding u-cast/m-cast/b-cast, auto learning as well as loading or editing entries (dynamic or static) into MAC or Multicast Tables.

- Flexible structure of the Switch allows meeting the customer needs by adding user blocks into Switch IP architecture to make a forwarding decision based on user’s criteria.

- Designed in System Verilog and targeting any RTL implementation.

- Supports External or Internal Host uPC.

Implementation Details

- Currently implemented on XCKU5P Kintex UltraScale+™.

- In progress migration to MPSoC ZU9EG/ ZU5EV Zynq UltraScale+™.

MPSoC ZU5EV is Xilinx Automotive XA Zynq® UltraScale+™ MPSoC family is qualified according to AEC-Q100 test specifications with full ISO26262 ASIL-C level certification.

Main application for this device is automotive ADAS (Advance Driver Assistance Systems), multimedia, surveillance, and other embedded video applications.

Configuration Options

- Number of external ports

- VLAN support

- MAC Table depth

- Packet Buffer depth

- Number of priorities per port

- System memory mapping